在摩爾定律逼近物理極限的今天,半導(dǎo)體行業(yè)正經(jīng)歷一場深刻的范式轉(zhuǎn)變。單純依靠晶體管微縮已難以持續(xù)滿足高性能、低功耗、異質(zhì)集成與小型化的需求。在此背景下,先進(jìn)封裝技術(shù)從幕后走向臺前,成為延續(xù)算力增長、驅(qū)動(dòng)系統(tǒng)創(chuàng)新的關(guān)鍵引擎。其發(fā)展路徑從傳統(tǒng)的2D平面封裝,演進(jìn)至當(dāng)前主流的3D立體集成,并正向著更具動(dòng)態(tài)自適應(yīng)潛力的4D封裝概念探索。這一演進(jìn)歷程不僅重塑了硬件的物理形態(tài),更對計(jì)算機(jī)軟硬件協(xié)同開發(fā)提出了全新的挑戰(zhàn)與機(jī)遇。

一、 二維(2D)封裝:系統(tǒng)級集成的基石

2D封裝是電子集成技術(shù)的傳統(tǒng)形態(tài),其核心特征在于所有芯片元件均水平布置在同一基板平面上,通過引線鍵合或倒裝焊等方式實(shí)現(xiàn)互連。隨著技術(shù)進(jìn)步,2D封裝也衍生出如扇出型晶圓級封裝(Fan-Out WLP)、嵌入式封裝等先進(jìn)形式,能夠在單顆封裝內(nèi)集成多個(gè)芯片(多芯片模塊,MCM),實(shí)現(xiàn)更高的I/O密度和更優(yōu)的電熱性能。

技術(shù)開發(fā)影響:在2D時(shí)代,硬件設(shè)計(jì)相對獨(dú)立,軟件架構(gòu)主要基于明確的芯片功能邊界和通信協(xié)議。封裝技術(shù)主要服務(wù)于物理連接和防護(hù),對軟件層的直接影響較小。硬件開發(fā)聚焦于單芯片性能提升和PCB板級系統(tǒng)設(shè)計(jì)。

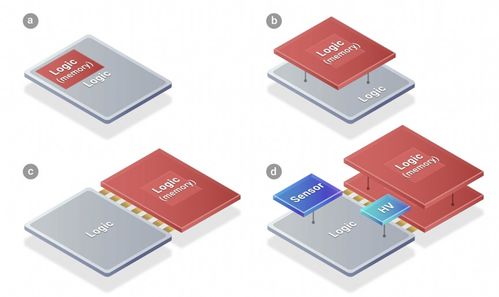

二、 三維(3D)封裝:垂直維度的革命

為突破互聯(lián)帶寬和延遲的瓶頸,3D封裝通過硅通孔(TSV)、混合鍵合(Hybrid Bonding) 等技術(shù),將多個(gè)芯片或芯片層在垂直方向上進(jìn)行堆疊與集成。這使得存儲單元可以緊鄰處理器(如HBM內(nèi)存與GPU的3D集成),信號傳輸路徑極大縮短,實(shí)現(xiàn)了超高帶寬、極低功耗和極致空間利用。3D集成可分為芯片堆疊(CoC)、晶圓堆疊(WoW)等多種形式,代表了當(dāng)前先進(jìn)封裝的主流方向。

技術(shù)開發(fā)影響:3D封裝對軟硬件開發(fā)帶來了根本性變革。

1. 硬件層面:設(shè)計(jì)必須從“平面思維”轉(zhuǎn)向“立體架構(gòu)”,需綜合考量熱管理(散熱成為嚴(yán)峻挑戰(zhàn))、應(yīng)力分布、測試策略以及異構(gòu)芯片(如邏輯、存儲、模擬)的垂直集成。EDA工具需支持3D設(shè)計(jì)與分析。

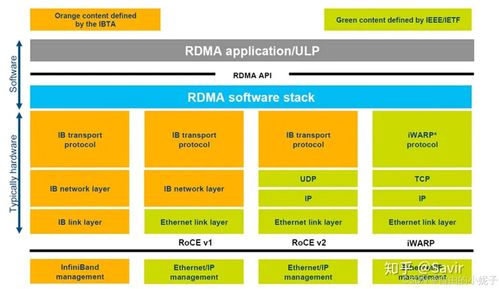

2. 軟件與系統(tǒng)層面:內(nèi)存與計(jì)算單元的緊耦合(如近存計(jì)算)要求操作系統(tǒng)、編譯器和應(yīng)用程序能夠感知并利用這種新的非均勻內(nèi)存訪問(NUMA)架構(gòu)。軟件需要優(yōu)化數(shù)據(jù)布局和任務(wù)調(diào)度,以充分發(fā)揮高帶寬、低延遲的垂直互連優(yōu)勢。硬件-軟件的協(xié)同設(shè)計(jì)(Co-Design)變得至關(guān)重要。

三、 四維(4D)封裝:面向未來的動(dòng)態(tài)智能集成

“4D封裝”是一個(gè)前瞻性概念,目前尚無統(tǒng)一定義,但其核心思想是在3D靜態(tài)堆疊的基礎(chǔ)上,引入動(dòng)態(tài)可重構(gòu)或自適應(yīng)的能力。這里的“第四維”通常指代時(shí)間維度或功能可變性。可能的實(shí)現(xiàn)途徑包括:

- 可編程互連:利用相變材料、MEMS開關(guān)等技術(shù),實(shí)現(xiàn)封裝內(nèi)部互聯(lián)路徑的實(shí)時(shí)重配置。

- 自適應(yīng)熱管理:集成微流控通道或形狀記憶合金,根據(jù)溫度動(dòng)態(tài)調(diào)整散熱結(jié)構(gòu)。

- 自修復(fù)與自監(jiān)測:集成傳感器與執(zhí)行器,實(shí)現(xiàn)封裝內(nèi)部狀態(tài)的實(shí)時(shí)監(jiān)控及輕微損傷的自主修復(fù)。

- 功能可變芯片:與可重構(gòu)計(jì)算(如FPGA)相結(jié)合,使堆疊系統(tǒng)的功能能根據(jù)任務(wù)需求動(dòng)態(tài)改變。

技術(shù)開發(fā)影響:4D封裝將把系統(tǒng)智能和靈活性從板級、芯片級進(jìn)一步下放至封裝級。

1. 硬件開發(fā)將涉及多物理場(電、熱、力、流體)的深度融合設(shè)計(jì),以及新型智能材料與半導(dǎo)體工藝的集成,挑戰(zhàn)極大。

2. 軟件開發(fā)可能面臨一個(gè)底層硬件拓?fù)浠蛐阅軈?shù)可在一定范圍內(nèi)動(dòng)態(tài)變化的“活”的系統(tǒng)。運(yùn)行時(shí)系統(tǒng)(Runtime System)、中間件和編程模型需要支持硬件資源的動(dòng)態(tài)發(fā)現(xiàn)、配置與優(yōu)化,實(shí)現(xiàn)真正的“感知-計(jì)算-執(zhí)行”閉環(huán)。這或?qū)⒋呱碌?strong>自適應(yīng)計(jì)算范式。

四、 封裝演進(jìn)驅(qū)動(dòng)軟硬件協(xié)同新生態(tài)

從2D到3D,再到展望中的4D,先進(jìn)封裝技術(shù)的每一次維度拓展,都是對系統(tǒng)性能瓶頸的一次突圍,也是對“計(jì)算”形態(tài)的一次重塑。其發(fā)展軌跡清晰地表明,硬件的創(chuàng)新已從單純的晶體管尺度驅(qū)動(dòng),轉(zhuǎn)變?yōu)?strong>系統(tǒng)級架構(gòu)、集成方法與材料科學(xué)的協(xié)同驅(qū)動(dòng)。

與此軟硬件邊界日益模糊。封裝不再只是被動(dòng)的“外殼”,而逐漸成為具備特定系統(tǒng)功能、甚至智能屬性的主動(dòng)“平臺”。這就要求未來的技術(shù)開發(fā)必須采用更緊密的跨層級協(xié)同設(shè)計(jì):芯片架構(gòu)師、封裝工程師、系統(tǒng)散熱專家、EDA工具開發(fā)者、操作系統(tǒng)內(nèi)核開發(fā)者乃至應(yīng)用程序優(yōu)化專家,需要在一個(gè)更早的階段進(jìn)行深度對話與聯(lián)合創(chuàng)新。

先進(jìn)封裝正在書寫電子系統(tǒng)集成的新篇章,它不僅決定了硬件能走多快、多小、多強(qiáng),更在定義著軟件如何思考、如何與硬件共舞。這場從二維平面到多維智能空間的旅程,將共同塑造下一代計(jì)算技術(shù)的全新面貌。